## Master's Thesis

in the Course of Study Computer Science

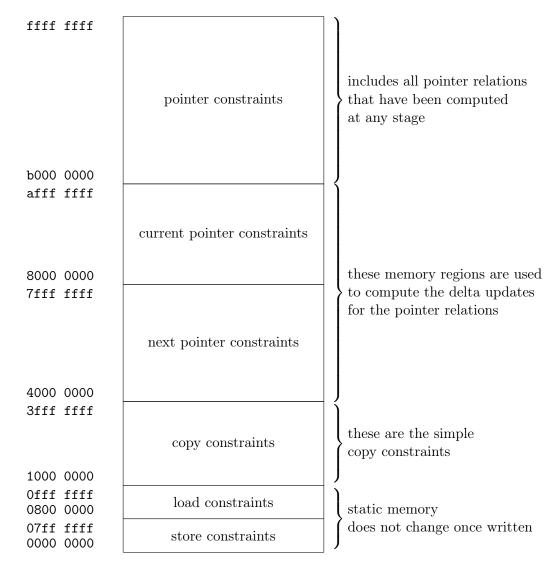

in Partial Fulfillment of the Requirements for the Degree Master of Science

# Implementing a parallel Points-To Analysis

Submitted by

## Lukas Böttcher

Matr. Nr.: 1125862 stu210239@mail.uni-kiel.de

at the Kiel University

| University supervisors: | Prof. Dr. Dirk Nowotka              |

|-------------------------|-------------------------------------|

|                         | DiplInf. Philipp Maximilian Sieweck |

|                         |                                     |

| Version from:           | July 9, 2024                        |

# Declaration

I hereby declare that the work presented in this thesis is entirely my own and that I did not use any other sources and references than the listed ones. I have marked all direct or indirect statements from other sources contained therein as quotations. Neither this work nor significant parts of it were part of another examination procedure. I have not published this work in whole or in part before. The electronic copy is consistent with all submitted copies.

place, date, signature

# Abstract

Pointer analysis is a subgroup of static analysis techniques. In general, the goal is to detect a set of memory locations for each pointer element in a program. All major compiler systems make use of this information in order to optimize the given code during compilation and most importantly, to detect errors in the program. In this thesis an interprocedural inclusion-based pointer analysis, PTAGPU, is presented that utilizes the parallel execution of GPGPUs to speed up the pointer analysis as part of the SVF framework. As the SVF framework itself is built on top of the LLVM compiler infrastructure, it is possible to run the proposed analysis on any program that can be compiled inside the LLVM toolchain. A meaningful speedup was observed with the proposed parallel implementation compared to the single threaded highly optimized wave propagation inclusion-based pointer analysis. An evaluation of the proposed analysis is provided both through the SVF test suite and a collection of open source programs used as benchmarks.

Keywords: pointer analysis, static analysis, GPU acceleration

# Acknowledgment

I would like to thank the dependable systems working group of the department of computer science at the Christian-Albrechts university for accommodating this master thesis and providing the hardware required to perform research for this thesis. Special thanks to my advisor Philipp Sieweck for providing guidance during the work on this thesis.

# Contents

| D | eclar | ation  |                                                      | Ι   |

|---|-------|--------|------------------------------------------------------|-----|

| A | bstra | ict    |                                                      | III |

| A | cknov | wledgr | nent                                                 | v   |

| 1 | Intr  | oduct  | ion                                                  | 1   |

|   | 1.1   | Struct | cure of this Thesis                                  | 1   |

|   | 1.2   | Motiv  | ation                                                | 2   |

|   |       | 1.2.1  | Static Analysis in Software Development              | 2   |

|   | 1.3   | Pointe | er Analysis                                          | 3   |

|   |       | 1.3.1  | Notions of Sensitivity in Pointer Analysis           | 4   |

|   |       | 1.3.2  | Andersen's Analysis                                  | 9   |

|   |       | 1.3.3  | Steensgard's Analysis                                | 10  |

|   |       | 1.3.4  | Wave Propagation                                     | 12  |

|   |       | 1.3.5  | LLVM - Generating Data for the Analysis              | 12  |

|   | 1.4   | Conte  | xt-free Languages                                    | 19  |

|   |       | 1.4.1  | Definition of Context-free Languages and Grammars    | 19  |

|   |       | 1.4.2  | Andersen Analysis via CFL-Reachability               | 21  |

|   |       | 1.4.3  | Context-free Path Queries via Matrix Multiplications | 22  |

|   | 1.5   | Relate | ed Work                                              | 27  |

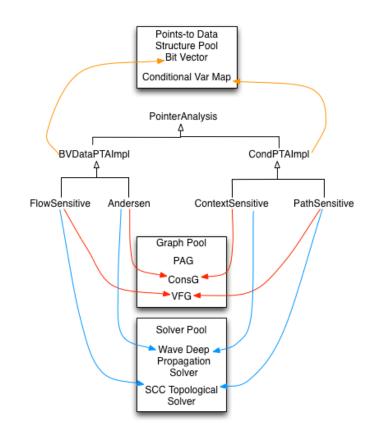

|   |       | 1.5.1  | SVF                                                  | 27  |

|               |        | 1.5.2   | Graspan                           | 30 |

|---------------|--------|---------|-----------------------------------|----|

| <b>2</b>      | PTA    | AGPU    |                                   | 33 |

|               | 2.1    | Integr  | ating PTAGPU into SVF             | 33 |

|               | 2.2    | Goal o  | of the Algorithm                  | 34 |

|               | 2.3    | Desigr  | a of the Algorithm                | 35 |

|               |        | 2.3.1   | CUDA Architecture                 | 35 |

|               |        | 2.3.2   | Initialization of CUDA code       | 40 |

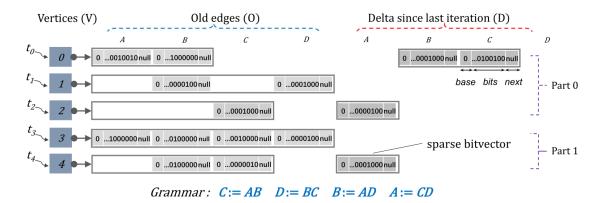

|               |        | 2.3.3   | Sparse bit vectors                | 42 |

|               |        | 2.3.4   | Edge Insertion                    | 44 |

|               |        | 2.3.5   | Concurrent Graph Rewriting        | 46 |

|               |        | 2.3.6   | Combining CPU and GPU execution   | 54 |

|               |        | 2.3.7   | Feeding the Results back into SVF | 56 |

|               | 2.4    | Exper   | imental Results                   | 56 |

|               |        | 2.4.1   | Test Suite                        | 57 |

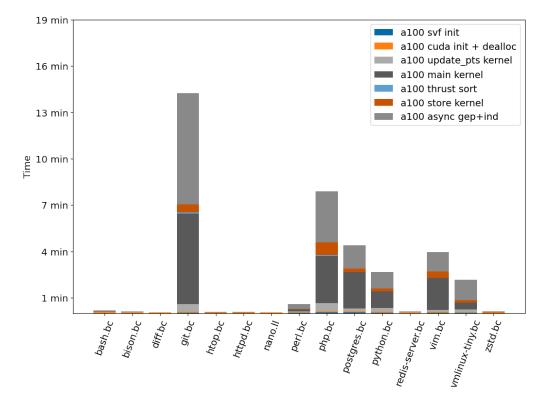

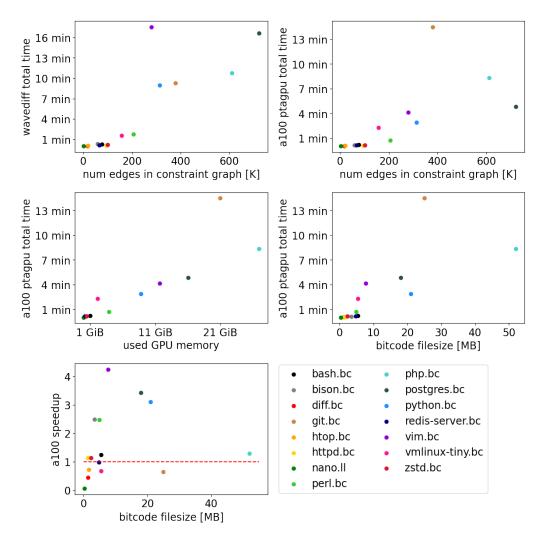

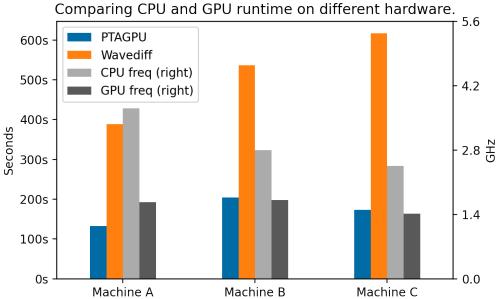

|               |        | 2.4.2   | Benchmark Suite                   | 58 |

| 3             | Dise   | cussior | 1                                 | 69 |

|               | 3.1    | Evalua  | ation of Results                  | 69 |

|               | 3.2    | Future  | e Work                            | 71 |

|               | 3.3    | Conclu  | ision                             | 73 |

| A             | Rav    | v Data  |                                   | 75 |

| $\mathbf{Li}$ | st of  | Figure  | es                                | 79 |

| Li            | st of  | Table   | 5                                 | 81 |

| Bi            | ibliog | graphy  |                                   | 85 |

# Chapter 1

# Introduction

The goal of this thesis is the implementation of a parallel pointer analysis. As well as researching to what extent such an implementation presents advantages or disadvantages over other pointer analyses that are not strictly parallel in nature.

A digital version of this thesis together with the full source code of the developed software is available online at https://git.informatik.uni-kiel.de/stu210239/masterarbeit.

## 1.1 Structure of this Thesis

This thesis is divided into three chapters. The first chapter, chapter 1, lays the groundwork for the implementation and goes into detail what ideas were pursued in order to develop the implementation. All related current work and its influences on this thesis are discussed here, as well as the motivation for the implementation itself. Furthermore, the fundamentals of pointer analysis are explained here with code samples and an end to end analysis workflow that aims to illustrate the connection between actual code and its representation in a pointer analysis.

In the second chapter, chapter 2, the software, namely PTAGPU, that was developed as part of this thesis, is described in detail. Design decisions, integrations with other software libraries and correctness are elaborated here. The experimental benchmark results and how they were generated are also presented here.

The last chapter, chapter 3, covers possible future work that could further improve the implementation and explore more ideas concerning parallel pointer analyses. This chapter also discusses the experimental results from chapter 2.

### 1.2 Motivation

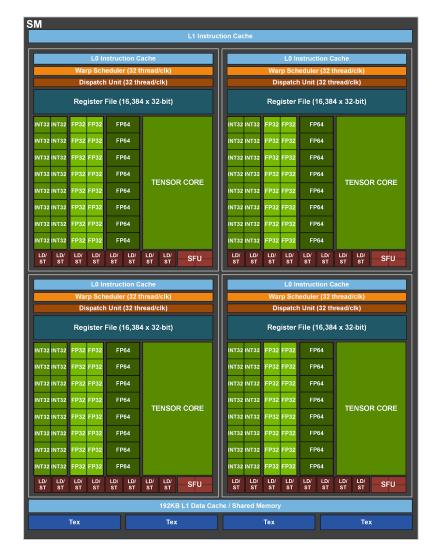

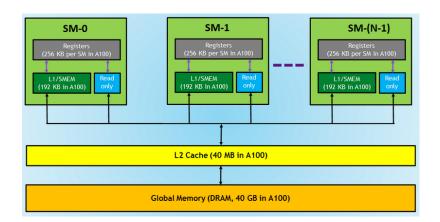

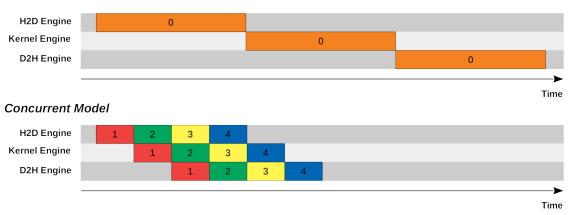

This thesis aims to explore the possibilities of parallelizing the Andersen style inclusionbased whole program pointer analysis. Specifically the goal is to improve static pointer analysis performance by using massively parallel GPGPUs. With the general trend of more complex software systems in software development, developers also require static analysis tools that are able to perform scalable analyses on entire codebases. Unfortunately general pointer analysis is an undecidable computational problem [Lan92], which prevents fully precise pointer analyses from being a possibility. For this reason all pointer analyses are approximate, and a balance must be found between performance and precision when analyzing code. Historically most pointer analyses are challenging to parallelise [SYXL15]. By using GPGPUs the proposed library from this thesis aims to improve performance when analyzing entire programs by distributing the work across the many streaming processors modern GPGPUs possess. The performance improvement of the proposed implementation also should not decrease the analysis precision.

#### 1.2.1 Static Analysis in Software Development

Currently, most compilers employ almost entirely intraprocedural pointer analyses to allow for a fast and scalable static analysis during compilation. Only recently limited support for interprocedural analyses was introduced in the GCC compiler<sup>1</sup>. With greater complexity in modern software projects, these ad hoc intraprocedural analyses during compilation are not sufficient for finding most bugs because they suffer from low accuracy and missing semantic information [GZJ+20]. Especially if a software project is composed of many components, interprocedural analysis is required for finding bugs that arise from interactions between individual components. One such project is the Linux kernel, which consists of a number of subcomponents that handle various parts of the kernel, such as drivers, cryptography and file systems. While utilizing static analysis tools on the Linux kernel is nothing new, precise interprocedural analysis still is a challenging problem for almost 30 million lines of code in the Linux kernel. For this reason this thesis explores options for improving scalability and performance of pointer analysis methods.

<sup>&</sup>lt;sup>1</sup>https://gcc.gnu.org/onlinedocs/gcc-12.2.0/gcc/Static-Analyzer-Options.html

### 1.3 Pointer Analysis

In general a pointer analysis tries to find the values of pointers in a program at runtime, without having to execute the program. So naturally this problem is undecidable [Lan92] following a reduction from the halting problem. As a result, performing a pointer analysis becomes a delicate balancing act between precision and performance. Commonly, analyses produce over-approximations of the targets each pointer can point towards at runtime while other parts of an analysis might omit or under-approximate certain parts for the sake of performance and scalability. As a result, these analyses are strictly speaking unsound or soundy as put forward by [LSS+15]:

"We introduce the term soundy for such analyses. The concept of soundiness attempts to capture the balance, prevalent in practice, of over-approximated handling of most language features, yet deliberately under-approximated handling of a feature subset well recognized by experts. Soundiness is in fact what is meant in many papers that claim to describe a sound analysis. A soundy analysis aims to be as sound as possible without excessively compromising precision and/or scalability." [LSS+15]

Pointer analyses build the foundation for a variety of other static analyses such as value-flow analyses, since call-graph generation is directly dependent on a prior pointer analysis in order to resolve indirect or dynamic calls statically. Without pointer information most static analysis algorithms are simply unable to reason about the state of a given program.

One common pointer analysis is the inclusion-based Andersen analysis [And94]. The details of this type of analysis will be discussed later on, as it is the underlying basis for the proposed algorithm in chapter 2. The Andersen algorithm sacrifices precision in favor of performance and achieves an upper bound of  $O(n^3)$  where n represents the number of pointer variables relevant to the analysis. This is known as the cubic bottleneck of general Andersen analysis [MP21]. This showcases the trade-off that all non-theoretical pointer analyses have to make in order to be applicable to real programs and avoid undecidability. Furthermore, Andersen's analysis is a P-complete problem and is therefore not trivially parallelizable [MP21].

As a general abstraction, pointer analyses can be seen as complex graph problems where programs are interpreted as graphs with nodes representing variables and edges representing relations between nodes, such as memory allocations and assignments between variables. This allows us to make use of a large body of previous research concerning graph problems and transform the general analysis into a better defined mathematical problem. Another analysis closely related to pointer analysis is alias analysis, where two pointers are said to alias if their points-to sets have an intersection. An alias analysis produces a set of relations over all nodes in the analysis graph where nodes can either **NotAlias**, **MayAlias** or **MustAlias**. For two given nodes, a, b and their points-to sets pts(a) and pts(b), the following constraints describe the relations.

$$a \text{ NotAlias } b \iff \forall ptd \in pts(a) \colon ptd \notin pts(b)$$

(1.1)

$$a$$

MayAlias  $b \iff \exists ptd \in pts(a) \colon ptd \in pts(b)$  (1.2)

$$a \text{ MustAlias } b \iff \forall ptd \in pts(a) \colon ptd \in pts(b)$$

(1.3)

Both pointer analysis, alias analysis, and points-to analysis are all terms commonly used interchangeably in literature [Hin01]. From now on pointer analysis will be used in this thesis to refer to this type of static analysis from which an alias relation can be derived based on the pointer information.

A motivating example for pointer analyses is the detection of memory leaks in programs. This occurs when a memory location is allocated on the heap, for example with a call to **malloc** in glibc, and is not freed at a later stage in the program. It is in the interest of the developer to find such faults as to not exhaust the computer's memory during execution by repeatedly allocating memory in the heap without freeing previous allocations. Finding such logical errors can be accomplished via a related static analysis called data-flow analysis, that tries to determine where specific data might flow in a program. Here pointer information is vital, as pointers can represent lateral movement of data through the control flow of a program, independent of direct assignments and read operations. Ultimately almost all static analyses require some kind of information about pointers to fully determine the state of a program. Aside from error detection such as memory leaks, optimizations are another aspect of compiler systems, where pointer information is important to achieve better results, see Listing 1. More often than not the pointer information alone does not provide an immediate value to the compiler or analysis tool, instead other procedures build on top of this information to derive valuable information about a program.

#### 1.3.1 Notions of Sensitivity in Pointer Analysis

As previously established, a complete general pointer analysis is undecidable. For this reason there are various notions of sensitivity when talking about pointer analysis. These notions represent a compromise between precision, scalability and complexity of the analysis. Following, some of the more common sensitivity notions will be illustrated to differentiate

```

#include <stdlib.h>

void *iter;

iter = value;

/* depending on the data at value's memory location

the loop might not be necessary */

while(*iter)

{

complex_computation(iter);

}

```

Listing 1: Optimizations in a c program

```

int a;

char b;

struct Person {

char *name;

int *age;

} p1, p2;

p1.age = &a; // the analysis can differentiate between p1.age and p1.name

p1.name = &b;

```

Listing 2: Field-sensitivity by example

the more complex analyses from the less complex analyses and explain the impact of these sensitivities on actual performance when analyzing a program.

#### **Field-sensitivity**

Field-sensitivity describes how the pointer analysis algorithm handles structures in the program. Most programming languages that expose memory management to a developer, such as C, C++ or Rust, offer some form of structures to represent an object that internally holds multiple values where these values might be pointers, that reference memory locations. If an analysis is field-sensitive, each field of each struct is represented in the analysis as an independent node that can point to unique memory locations, as long as the field can be statically determined during the analysis, see Listing 2. If the field of a struct can not be statically determined, for example because of an arithmetic operation that produces multiple possible results for the offset during runtime, it is common for field-sensitive pointer analyses to fall back to a field-insensitive mode for the specific struct, wherein all fields of the struct are merged into a single abstract object. For the given example, p1.age and p1.name can point to different memory locations.

does not differentiate between any fields of a given struct at any point of the analysis. Therefore, only two nodes are created to represent the struct, p1.\* and p2.\*. Another common alternative is field-base-sensitivity, where instead of omitting the individual fields of each struct, the fields of every struct are merged into a single instance of that struct. As a result the Person structs, p1 and p2, would be represented as a single object with fields name and age, such that p1.age == p2.age are represented by the same node in the analysis.

#### Array-sensitivity

Array-sensitivity is conceptually similar to field-sensitivity but often has different effects on the runtime of the analysis. For a given array intarr[100] an array-sensitivie analysis would model each entry of the array, e.g. arr[0], arr[1], ..., with a unique node, whereas an insensitive analysis would model the array as a single node. Generally speaking arrays are often homogeneous data structures that can hold a vast amount of data, compared to structs which are often more compact as they model attributes instead of raw data. Therefore, array-sensitivity if often omitted from whole program analyses, while field-sensitivity is common among pointer analyses.

#### Scope of the analysis

When designing a pointer analysis one has to make a decision about how to handle external code that the program depends on. Often times transitive dependencies of a program can dwarf the original code by several magnitudes in size [TG17]. Even a basic Hello World program in Java transitively depends on 3000 classes [KMZN16] from the Java standard library. For this reason most analyses either ignore external library code during analysis, or stub the most relevant library calls during analysis, such as malloc or free. This trade-off is well worth it, as most interesting properties in pointer analysis do not originate in external libraries, but the actual program code that is written by the developer. This does however not solve the problem of standard library code mutating the program state either via callbacks or mutation of values behind pointer arguments. Here, simply ignoring the external code during analysis would greatly decrease the accuracy of the analysis. For this reason, a lot of research is being done to develop methods that alleviate some of the problems that arise from analyzing external dependencies of a given program. Caching incremental results during analysis seems to be one of the most promising methods thus far [MGR13], where instead of solving the pointer analysis problem from the top-down, the analysis begins at the bottom and builds summaries for functions incrementally until a

```

int *manupulatePointer(int *ptr);

int main() {

int *a, *b;

b = manupulatePointer(a);

/* intraprocedural analysis is unable

to determine the state of a or b */

}

```

Listing 3: Limitations of intraprocedural analysis

result over the entire program is achieved. Hybrid approaches combining top-down and bottom-up analysis represent state-of-the-art analysis methods in use by production static analysis tools, such as Coverity [MGR13].

#### Interprocedural analysis

Another aspect that greatly influences the precision of analyses is whether they are interprocedural or intraprocedural. An intraprocedural analysis only analyzes each function in an isolated context and disregards any influences on other functions or global state. Interestingly most compilers rely mostly on intraprocedural analysis for bug detection as it can be performed in parallel for each function independently and is in general much faster than interprocedural analysis. The following example Listing 3 illustrates the shortcomings of only performing intraprocedural analysis. Essentially parameter passing, especially of pointers, is not taken into account properly for the calculation of points-to sets. An interprocedural analysis overcomes these limitations by connecting parameters of functions and the arguments at the respective call-sites as well as the resulting return values in the graph structure that is used to solve the pointer analysis. Fundamentally an interprocedural analysis is related to another notion of sensitivity, context sensitivity, since every context-sensitive analysis has to be interprocedural in order to capture the context of each function call [Lin15].

#### Flow-sensitivity

When one performs a flow-sensitive pointer analysis, this means that the analysis takes into account the control flow of the program when calculating points-to information. As can be seen in Listing 4, a flow-sensitive analysis is in general more precise than a flowinsensitive analysis. Meanwhile, running a flow-sensitive analysis can also be exponentially more expensive to compute as every step in a programs control flow carries its own state concerning points-to relations - especially when the control flow is complicated by complex

```

int *manupulatePointer(int *ptr);

int main() {

int a, b, *x; // x -> {}

if (something())

x = &a; // x -> {a}

else

x = &b; // x -> {a,b} ?

manupulatePointer(x);

/* a flow insensitive analysis computes

a points-to set {a,b} for x while in actuality

x = &b and x = &a are mutually exclusive statements

during execution */

}

```

Listing 4: Flow-sensitivity by example

conditional statements or recursive execution. Although this problem can be slightly alleviated, by only considering program statements that manipulate pointers. Empirical studies have shown that for context-insensitive analyses, adding flow-sensitivity to the points-to calculation does not offer a significant precision improvement over flow-insensitive analyses [Hin01]. This makes using a flow-sensitive analysis without context-sensitivity unattractive as an initial analysis run. One should rather combine context- and flowsensitivity in subsequent analysis runs to refine the initial points-to results in certain regions of code that profit from a further refinement. Using a flow-sensitive pointer analysis also generates must-alias relations, compared to the comparatively imprecise may-alias relations from a flow-insensitive pointer analysis. Generating definitive information that two variables will unconditionally alias during runtime is very valuable when considering refactoring optimizations by a compiler. While a sound may-alias analysis requires that no possible alias relations are missed, a sound must-alias analysis requires analogously that no spurious alias relations are reported. Both are respectively over- and under-approximations of the true points-to results.

#### **Context-sensitivity**

As previously alluded to, context-sensitivity is directly related to interprocedural analyses, since it governs how call sites and called functions are interpreted during the analysis. More specifically a context-sensitive analysis tries to qualify variables both on the heap and stack with contextual information such that different contexts can be established, where for example points-to information for a variable differs, thus improving the precision of the analysis. To achieve this, context-sensitivity can be modeled by using call-sites and

```

int *manupulatePointer(int *ptr);

int main() {

int a, b, *x;

x = &a;

manupulatePointer(x);

x = &b;

manupulatePointer(x);

/* a context-sensitive analysis evaluates both

calls to manupulatePointer as unique function calls

since the context differs between both calls */

}

```

Listing 5: Context-sensitivity by example

objects to differentiate and qualify the context for variables [SB+15]. Depending on the programming language at hand, these methods can yield different precision. It has been established that object-oriented languages like Java greatly benefit from object-sensitivity over call-site-sensitivity, while more procedural languages like C benefit from call-site-sensitivity. While a context-sensitive analysis would in theory provide more precision and therefore decrease the average size of points-to sets, in practice most context-sensitive pointer analyses, when applied to sizeable codebases, quickly grow out of control as the analysis explodes in terms of running time and space requirements [SKB14]. In contrast, context-insensitive analyses anecdotally scale better than context-sensitive analyses.

#### 1.3.2 Andersen's Analysis

Andersen's analysis is an inclusion-based interprocedural pointer analysis algorithm first proposed by [And94] in 1994. It is a field-sensitive, context-insensitive and flow-insensitive analysis. The algorithm was one of the first constraint based algorithms introduced for pointer analysis. Since it is lacking constext- and flow-sensitivity, it is often used as a base algorithm which produced broad over estimations of the points-to data and is later refined by more precise algorithms which improve the quality of the data and remove false positives from the points-to information generated by Andersen's algorithm. The underlying idea is that the Algorithm operates on a given program by converting statements from the program into mathematical constraints contained in a constraint graph. These constraints can be classified into a few types which can be seen in Table 1.1. It is worth noting that in literature the field-sensitivity aspect is often omitted from the definition of the Andersen analysis, although it was included in the original specification. As mentioned in chapter 1 the complexity of Andersen's analysis grows exponentially with regard to the

| Statement | Name   | Description                             | Constraint                                            |

|-----------|--------|-----------------------------------------|-------------------------------------------------------|

|           |        |                                         | -                                                     |

| x = &a    | alloca | The address of a is assigned to x.      | $\{a\} \subseteq pts(x)$                              |

| x = y     | copy   | Variable y is assigned<br>to x.         | $pts(y) \subseteq pts(x)$                             |

| x = *y    | load   | Load value of y and assign to x.        | $\forall p \in pts(y) \colon pts(p) \subseteq pts(x)$ |

| *x = y    | store  | Store y into value of x.                | $\forall p \in pts(x) \colon pts(y) \subseteq pts(p)$ |

| x = y.f   | field  | Field f of variable y is assigned to x. | $pts(y.f) \subseteq pts(x)$                           |

Table 1.1: Constraints of an inclusion-based pointer analysis.

number of pointer variables in a program. The reason for this exponential growth, among other aspects, is the field-sensitivity. Depending on the structure of the code under analysis, field-sensitivity might play the most influential part in the analysis' complexity. This will be further expanded upon in chapter 2. Ultimately this is the reason for specifically including field-sensitivity when discussing Andersen's analysis in this thesis. During execution an Andersen style pointer analysis repeatedly applies the constraints until a point is reached where no more changes are applied to the constraint graph at which point the execution concludes and the points-to sets for each variable are returned.

### 1.3.3 Steensgard's Analysis

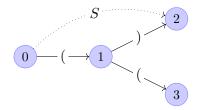

Steensgard's analysis was introduced in 1996 by [Ste96]. It was inspired by Andersen's analysis and as such is also an interprocedural pointer analysis. The key proposition of Steensgard's work was to improve the runtime of Andersen's algorithm by using equalities instead of subsets for the constraints that are used as inputs for the algorithm, an overview for the constraints can be seen in Table 1.2 - the rules are nearly identical to the constraints for the Andersen algorithm. The change from subsets to equalities leads to an almost linear algorithm by utilizing union/find data structures for efficient computation of a fixpoint solution for a given set of pointers. The trade-off for this faster algorithm is precision, since Steensgard's algorithm quickly loses precision compared to Andersen's algorithm by losing the small differences between points-to sets of individual variables by equating them. An example for this precision loss can be seen in Listing 6.

```

int main() {

int a, b, *x, *y;

x = &a; // pts(x) = {a}

y = &b; // pts(y) = {b}

y = x; // pts(y) = pts(x) = {a,b}

/* by equating the points-to sets of x and y

the fact that x never points to b is lost

this leads to an obvious loss of precision */

}

```

| Statement               | Name   | Description                              | Constraint                                                                      |

|-------------------------|--------|------------------------------------------|---------------------------------------------------------------------------------|

| x = &a                  | alloca | The address of a is                      | $pts(x) = \{a\} \cup pts(x)$                                                    |

| $x = \infty x$<br>x = y | copy   | assigned to x.<br>Variable y is assigned | pts(y) = pts(x) $pts(y) = pts(x)$                                               |

| x = y<br>x = *y         | load   | to x.<br>Load value of y and             | $\forall p \in pts(y) : pts(p) = pts(x)$                                        |

| x = *y $*x = y$         | store  | assign to x.<br>Store y into value of x. | $\forall p \in pts(y): pts(p) = pts(x)$ $\forall p \in pts(x): pts(y) = pts(p)$ |

| x = y.f                 | field  | Field f of variable y is assigned to x.  | pts(y.f) = pts(x)                                                               |

Table 1.2: Constraints of an equality-based pointer analysis.

### 1.3.4 Wave Propagation

Since its first introduction in 1994, there have naturally been many incremental improvements to the Andersen style pointer analysis. Most current implementations are derived from [PB09], specifically the Wave Propagation Method, which is a highly optimized version of Andersen's algorithm. In Wave Propagation the procedure is separated into an insertion phase and a propagation phase. Furthermore, the constraint graph is topologically sorted and acyclic, which enables the algorithm to pass forward the computed points-to information in topological order, preventing redundant work since only set differences need to be propagated to the next nodes. The algorithm is intended to be more memory intensive in order to achieve better performance on large codebases [PB09]. The general algorithm for wave propagation is listed in Algorithm 1.

### 1.3.5 LLVM - Generating Data for the Analysis

By now the fundamentals of pointer analysis have been introduced, which unilaterally can be modeled as a graph problem. The missing part of the introduction is where the underlying data for such a pointer analysis algorithm comes from or how it is derived from a given program that has to be analyzed. Initially pointer analyses were solely implemented in compilers to detect errors and find possible optimizations during compilation. As compilers already employ an internal representation for the programs to be compiled, the data generation was not problematic. As the scope of pointer analyses expands from intraprocedural analysis part of a compiler towards standalone interprocedural whole program analyses, it is clear, that a new representation for programs is needed, on which analyses can run - independent of the compilation process.

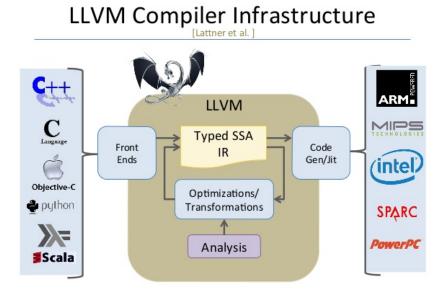

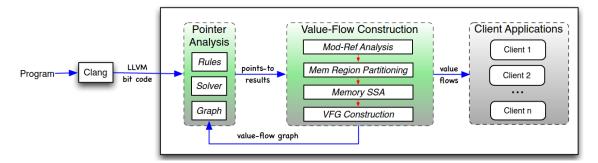

During initial review of literature for pointer analysis multiple methods for data generation were surveyed. Notably, simply parsing the source code was among the most common data extraction methods for programs. Another method was to extract an intermediate representation, called LLVM-IR, of the code during initial compilation of a program by means of using the low level virtual machine, LLVM. Using LLVM has some distinct advantages compared to parsing the source files of a program directly. For one, LLVM provides multiple compiler front-ends for various compiled programming languages, including C/C++ and Objective-C through the Clang compiler or Rust through the rustc compiler, which allows one to compile multiple languages without having to adapt the parser, as can be seen in Figure 1.1. Especially when working with older non-strictly standardized versions of the C language, utilizing all available tricks of an established compiler proves to be more resourceful compared to reinventing the wheel with new parsing tools. Secondly

```

Algorithm 1 General Wave Propagation Algorithm

Input: Constraint Graph G = (V, E)

Output: Modified Constraint Graph G = (V, E) and points-to information.

```

```

Detect strongly connected components and find topological sorting for G.

Build topological node stack T.

repeat

changed = False

worklist = \emptyset

while T \neq \emptyset do

node \leftarrow pop from T

for edge (node, target) \in out_{copy/gep}(node) do

pts(target) \leftarrow union pts(node) pts(target)

if pts(target) changed then

changed = True \wedge add target to worklist

end if

end for

end while

while worklist \neq \emptyset do

node \leftarrow pop from worklist

for edge (node, target) \in out_{load}(node) do

for ptsDst \in pts(node) do

add copy edge (ptsDst, target) to G.

if edge added to G then

changed = True

end if

end for

end for

for edge (src,node) \in in_{store}(node) do

for ptsDst \in pts(node) do

add copy edge (src, ptsDst) to G.

if edge added to G then

changed = True

end if

end for

end for

end while

if Edge added to G then

changed = True

end if

until changed = False

```

Figure 1.1: Illustration of the LLVM toolchain from Lattner et al.

one can easily verify the correctness of the extracted data for a program by simply executing the compiled intermediate representation since no matter the programming language, as part of the LLVM toolchain the program always gets compiled into the intermediate representation before being assembled and linked. The LLVM project provides specific tools for executing programs in LLVM-IR format using a just-in-time compiler <sup>2</sup>. Beyond the binary intermediate representation, also called bitcode, there exists a human-readable format. Both binary and text versions can be converted between with the LLVM tools <code>llvm-as</code> and <code>llvm-dis</code>, see Listing 7 for a basic hello world program in human-readable LLVM-IR.

### LLVM Instructions

With the generated LLVM-IR we can now build a graph, by interpreting the individual LLVM instructions as constraints for a chosen pointer analysis. The LLVM-IR uses static single assignment (SSA) form for variables meaning that each variable can only be assigned a single time in a specific control flow in the intermediate representation. The use of SSA form is not directly relevant to Andersen style analyses but simplifies working with variables conceptually, since no variable can be reassigned at any point of the program. At this point it is also important to differentiate between address-taken variables and top-level variables. Top-level variables' values reside in registers and are conceptually ephemeral

$<sup>^{2}</sup> https://releases.llvm.org/9.0.1/docs/CommandGuide/lli.html$

```

#include <stdio.h>

int main()

{

int i;

i = 10;

printf("Hello World! N = %d\n", i);

return 0;

}

// gets compiled into...

@.str = private unnamed_addr constant

[21 x i8] c"Hello World! N = %d\0A\00", align 1

; Function Attrs: noinline nounwind optnone uwtable

define dso_local i32 @main() #0 {

\%1 = alloca i32, align 4

\%2 = alloca i32, align 4

store i32 0, i32* %1, align 4

store i32 10, i32* %2, align 4

%3 = load i32, i32* %2, align 4

%4 = call i32 (i8*, ...) @printf(i8* getelementptr inbounds

([21 x i8], [21 x i8]* @.str, i64 0, i64 0), i32 %3)

ret i32 0

}

declare dso_local i32 @printf(i8*, ...) #1

```

Listing 7: A basic hello world program in human-readable LLVM-IR.

while address-taken variables are abstract memory objects which logically reside in memory. The specifics of memory locations and cpu registers are of course hardware specific and depend on the target architecture that the LLVM backend assembles the intermediate representation into. The connection between address-taken and top-level variables in the LLVM-IR is established by the alloca instruction which maps a top-level variable to a memory location represented by an address-taken variable. Following is an interpretation of the LLVM instructions for Andersen's pointer analysis.

**Alloca Instruction** The LLVM **alloca** instruction is used to allocate memory on the stack.

```

; allocate a pointer to a 32 bit integer on the stack

; and save a reference at ptr

%ptr = alloca i32*, align 8

```

The analog of the alloca instruction in a pointer analysis is the address-of operation x = &a, since the top-level variable *ptr* points to the abstract memory location holding the actual value. This might come as a surprise, since the implementation of x = &a in C does not result in an alloca instruction in the LLVM-IR. This often leads to confusion when interpreting points-to results that are built using the LLVM-IR. Nonetheless the interpretation of the alloca instruction as an address-of pointer constraint is in line with the constraints of the Andersen algorithm.

**Load Instruction** The LLVM load instruction loads the value of a top-level variable into a new variable. Compared to the C programming language this is comparable to dereferencing a pointer variable.

```

%ptr = alloca i32*, align 8

; load the pointer to the 32 bit integer from ptr into %var

%var = load i32*, i32** %ptr, align 8

```

When interpreting LLVM load instructions for a pointer analysis, we can treat it as the complex load constraint that is already defined for Andersen's analysis in Table 1.1. Again, just like the **alloca** instruction, we can not draw a direct comparison between the definition of the constraint x = \*y and the equivalent statement in the C language, since we are working with the LLVM-IR in SSA form. The C equivalent of the **load** instruction would be the dereferencing of \*y alone. The assignment to x would require another **store** instruction.

**Store Instruction** The LLVM **store** instruction stores a value into a variable. The variable might be a top-level or an abstract memory object represented by an address-taken variable.

```

%ptr = alloca i32*, align 8

%var = load i32*, i32** %ptr, align 8

; store the literal value 10 into %var

store i32 10, i32* %var, align 4

```

The interpretation of the LLVM store instruction is similar to the load instruction. It can be interpreted as the complex store constraint defined as part of Andersen's analysis.

**Getelementptr Instruction** The LLVM getelementptr or gep instruction is used to get subelements from an aggregate data structure such as arrays or structs. When the gep instruction is invoked, it requires an index in order to perform the address calculation for the subelement. Getelementptr does not access memory, it only finds the correct address given a variable and an index.

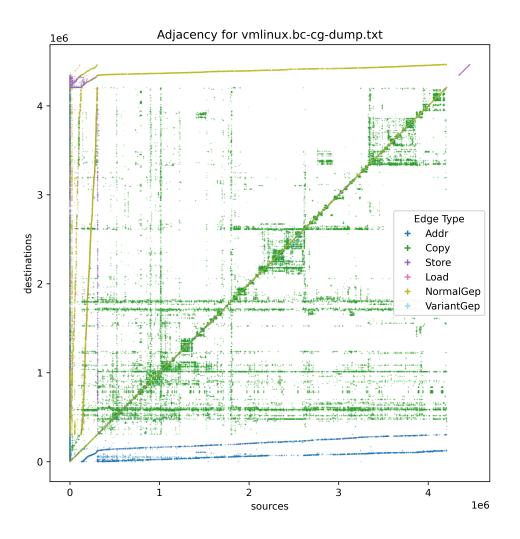

Since we intend to run a static analysis, we need to consider the properties of the index value passed into the getelementptr instruction. Either the index is a constant value, and we can forward the gep instruction together with the constant index into the static analysis, or the index is a variable that is subject to change during execution, and we need to assume that every possible value can be realized during execution, i.e. every offset for an aggregate data structure might be referenced by such a gep instruction and this information must be passed to the static analysis. This behavior is handled by differentiating between two types of gep constraints in the pointer analysis, normal- and variant-gep constraints. The former specifying a singular offset and the latter every possible offset for a given aggregate data type, since the value can not be statically determined.

**Copy Instruction and equivalent Instructions** Other than the complex store, load and the address-of constraints, the Andersen inclusion-based pointer analysis operates also on simple constraints, see line 2 in Table 1.1. In terms of LLVM-IR instructions, we are only interested in those instructions that manipulate pointers. In the LLVM-IR specification lots of instructions can result in values being moved, including pointers. Therefore, we group those instructions that can move values between symbols under the simple inclusion-based copy constraint. The following instructions are interpreted as simple copy constraints:

- Phi instructions are part of the LLVM-IR to correctly resolve control flow. Depending on the conditional branch a new SSA variable is introduced that holds the resulting value from the branch. Since we are implementing a flow-insensitive pointer analysis we do not differentiate between control flows and simply interpret each phi instruction as a simple constraint connecting the conditional values to the resulting phi variable.

- Select instructions serve a similar purpose as phi instructions. Here a value is selected conditionally without creating branches. As such we interpret the select instruction as a simple constraint.

- Call instructions represent a function call. If the function call contains arguments the caller arguments and callee parameters need to be interpreted as a simple constraint. Beyond this, nothing is done to analyze the context of the function call, since we are performing a context-insensitive pointer analysis.

- Like the call instructions, **ret** instructions are simply interpreted as simple constraints so the returned function value is included in the pointer analysis.

- ThreadFork ThreadJoin are not LLVM-IR instructions. But just like the call and ret instructions, these must be interpreted as function calls with simple constraints in the context of pointer analysis.

- Lastly there are various instructions that are straightforward to interpret as simple constraints, including bitcast, ptrtoint, constexpr, extractvalue and freeze instructions. Furthermore, variable argument values and external library call parameters need to be handled like regular call instructions.

Now with alloca, load and store instructions introduced, we can analyze a basic example by applying Andersen constraints to perform a pointer analysis. We are going to observe a simple c program, which will compile into the following LLVM-IR.

| <pre>int *p, x, *q;</pre> | %1 = alloca i32*, align 8         |  |  |  |  |  |  |

|---------------------------|-----------------------------------|--|--|--|--|--|--|

| p = &x                    | %2 = alloca i32, align 4          |  |  |  |  |  |  |

| q = p;                    | <b>%3 = alloca i32*, align</b> 8  |  |  |  |  |  |  |

|                           | store i32* %2, i32** %1, align 8  |  |  |  |  |  |  |

|                           | %4 = load i32*, i32** %1, align 8 |  |  |  |  |  |  |

|                           | store i32* %4, i32** %3, align 8  |  |  |  |  |  |  |

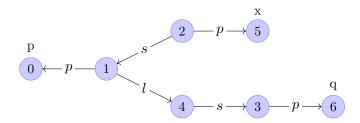

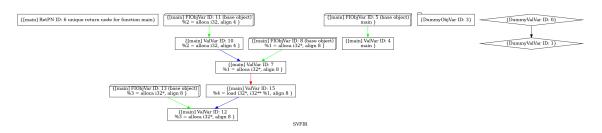

An example for applying the constraint rules according to the Andersen algorithm in Table 1.1 can be observed in Table 1.3. The edge labels of the constraint graph are p, s, l, c corresponding to points-to (inverse alloca), store, load and copy constraints. Furthermore, the copy edges are immediately converted into points-to edges in order to simplify the constraint graph in this example and reduce the number of steps.

### 1.4 Context-free Languages

Looking at the problem definition for an Andersen style pointer analysis, most algorithms in the literature operate on graph data structures. In this section we will look at an alternative interpretation of the pointer analysis problem where the problem can be solved by transforming it into a graph-reachability problem which can be solved by using contextfree languages, i.e. CFL-reachability. This approach was first introduced for static analysis purposes by [Rep98] and was found to be solvable in cubic time.

#### 1.4.1 Definition of Context-free Languages and Grammars

A context-free language is a language that can be generated by a context-free grammar. A context-free grammar is a 4-tuple  $CFG = (V, \Sigma, R, S)$  that holds a finite set of nonterminal characters V, a finite set of terminal characters  $\Sigma$ , a finite relation (rewrite rules) over  $V \times (V \cup \Sigma)^*$  and a start variable  $S \in V$ .

A prominent example for context-free languages is the balanced parenthesis language, which is defined by:

- 1.  $CFG_{bpar} = (V, \Sigma, R, S)$

- 2.  $V = \{S\}$

- 3. S = S

- 4.  $\Sigma = \{(,)\}$

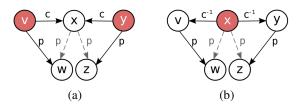

| Code Snippet to analyze / comment                                                                                           | Constraint Graph                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>%1 = alloca i32*, align 8 %2 = alloca i32, align 4 %3 = alloca i32*, align 8</pre>                                     | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| store i32* %2, i32** %1, align 8                                                                                            | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <pre>%4 = load i32*, i32** %1, align 8 store i32* %4, i32** %3, align 8 ; create constraints from every ; instruction</pre> | $\begin{array}{c} p \\ \uparrow \\ p \\ p \\ \downarrow \\ p \\ \downarrow \\ l^{\star} \\ \checkmark \\ $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| ; apply first store<br>; constraint rule(s)                                                                                 | $p \longrightarrow x  q$ $\uparrow \qquad \uparrow \qquad \uparrow \qquad \uparrow$ $p \qquad \downarrow$ $p \qquad \uparrow$ $p \qquad \downarrow$ $p  $ |